�a(ch��n)Ʒ���c��

��FPGA ���_���䡢FPGA ������̖��(chu��ng)����PCB ��BGA ���b�W(w��ng)�j(lu��)��(y��u)���ṩ�˼����O(sh��)Ӌ�h(hu��n)��

���FPGA���_�����cPCB���ֲ����O(sh��)Ӌ֮�g�Ę������ʹ������FPGA ���_�ķ����c��(y��u)������׃���p�����e

�ԄӸ�ۙHDL Դ���a��FPGA ���_���估PCB ��BGA �������_�B���P(gu��n)ϵ�ĸ�׃�����ʾ���P(gu��n)��(sh��)��(j��)�M��ͬ������

֧���O(sh��)Ӌ�ڲ�ͬF(xi��n)PGA ����֮�g����ֲ

�ɽY(ji��)��PCB �W(w��ng)�탞(y��u)��FPGA �����Ĺ��_���䣬֧�ֹ��_������Ϣ��IO Designer�������

ԭ��D��PCB �h(hu��n)���е��p����f

֧������FPGA �S�ҵ�����������������ݸ��NFPGA �_�l(f��)�h(hu��n)���ľC�ϼs���ļ�������ֲ����s���ļ����Ɍ�(d��o)���(y��u)�����еĹ��_������Ϣ

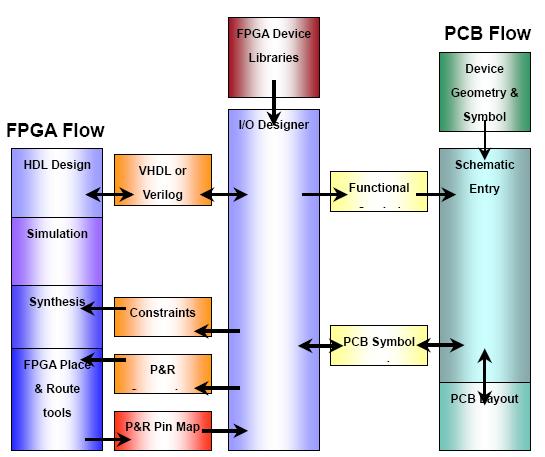

I/O Designer�����Ԅ��P(gu��n)(li��n)����ӱ����c�D�δ��ژ�(g��u)�ɵ�FPGA/PCB �����O(sh��)Ӌ�h(hu��n)������

FPGA/CPLD ����Ӯa(ch��n)Ʒ�O(sh��)Ӌ�еđ�(y��ng)�ü���V�������FPGA �cPCB ��ͬ���O(sh��)Ӌ�ѳɞ�I(y��)���ձ����R���y�}���O(sh��)Ӌ���̎���ҪͶ������ĕr�g���������(f��)��ͨ�ʹ_�J��FPGA ���_������Ϣ��������������©������FPGA ���_���x�cPCB �W(w��ng)�j(lu��)�B�ӵĔ�(sh��)��(j��)��һ��������Ķ���ɮa(ch��n)Ʒ�_�l(f��)���ڵ����`���O(sh��)Ӌ����(f��)���S��FPGA ����Ҏ(gu��)ģ���T��(sh��)/���_��(sh��)���������������ijЩ�������_��(sh��)���_1500 �����ϣ�F(xi��n)PGA �cPCB ��ͬ���O(sh��)Ӌ���}����ͻ��������

Mentor Graphics ��˾��I/O Designer �ǘI(y��)���(y��u)���FPGA/PCB ͬ���O(sh��)Ӌ�Ľ�Q������

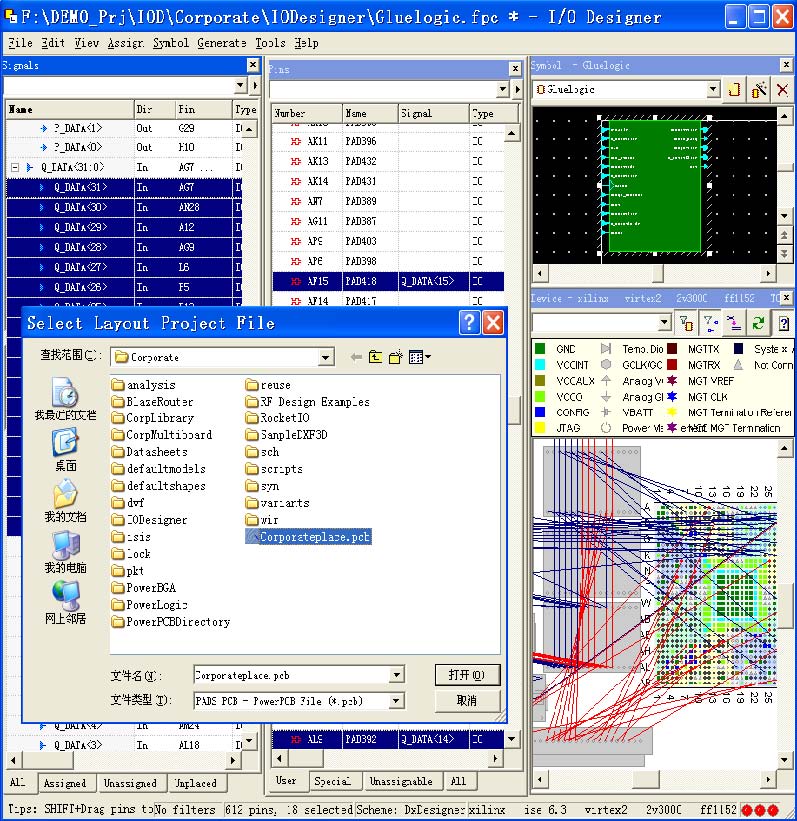

��I/O Designer �ļ��ɭh(hu��n)�����������O(sh��)Ӌ�߿��Ԍ�(d��o)��HDL �O(sh��)Ӌ�е���̖��FPGA �����Ĺ��_��Ϣ�c�O(sh��)Ӌ�s����Ϣ������ԭ�� �D��̖�����PCB ����ҕ�D�c�W(w��ng)�j(lu��)�B�ӵ��P(gu��n)�I��Ϣ������Ȼ���ֹ����Ԅӄ�(chu��ng)��HDL ��̖��FPGA ���_��ӳ������Ԅӄ�(chu��ng)����(f��)�sFPGA ������ԭ��D��̖�;W(w��ng)�j(lu��)������PCB���ֺ;W(w��ng)�j(lu��)�B��ҕ�D���{(di��o)���̓�(y��u)��FPGA ���_�������������(j��)��(y��u)����Ĺ��_���������FPGA �C�ϼs���Ͳ��ֲ����s����������_���O(sh��)Ӌ�F꠸�Ч��������L�U�،��F(xi��n)FPGA/PCB ��ͬ���O(sh��)Ӌ��

�ӑB(t��i)���_�����c��(y��u)��

I/O Designer �鄓(chu��ng)���c��(y��u)��FPGA ���_�����ṩ�˺���ֱ�^�IJ���������������O(sh��)Ӌ�߿ɶ��x��Ҏ(gu��)�t�����Ȼ��ͨ�^ܛ����HDL ��̖�Ԅӷ���FPGA ���_����Ҳ��ͨ�^���ε�����зŲ������F(xi��n)��һ��̖����FPGA ���_��ӳ������O(sh��)Ӌ��߀������ܛ����PCB ����ҕ�D������ֱ�ӿ���PCB �оW(w��ng)�j(lu��)�w�������r���������Դˁ��Ԅӻ��ֹ���(y��u)��FPGA ���_�ķ��䣬ÿ���Ĺ��_�����Ч��������ܛ���ЄӑB(t��i)���r���@ʾ����O(sh��)Ӌ�߿��Կ��ٶ��ʴ_�����FPGA ���_��(y��u)��������

��(sh��)��(j��)ͬ��������FPGA ��PCB ���O(sh��)Ӌ�����������HDL��̖�cFPGA ���_��ӳ����Ϣ��횇���һ��������I/O Designer �����ԄӸ�ۙ�������̌����_������Ϣ���ģ�����ʾ�������̼��r���������_�����_������Ϣ�������O(sh��)Ӌ�����е�һ����������������I/O Designer ֧���ֹ����Ԅ����HDL��̖��FPGA ���_��ӳ��������������(j��)ӳ��Y(ji��)����(chu��ng)��FPGA ���ֲ����s���ļ���Ȼ��Y(ji��)��HDL Դ�ļ��������ڰ弉�O(sh��)Ӌ��ԭ��D��̖�����Ԫ�����Լ����_���Ե���Ϣ����������⣬I/O Designer ߀���Ԍ�(d��o)��弉ԭ��D��PCB �O(sh��)Ӌ�Ќ����_������IJ����������_���Q��Pin Swap����߉�T���Q��GateSwap��������Ķ�����FPGA ���ֲ����s����

����FPGA/PCB ��ͬ���O(sh��)Ӌ������I/ODesigner ��һ���������Ҫ�һ�o���Ľ�Q�������������顰FPGA ���ֲ������s���ļ� ���弉PCB �O(sh��)Ӌ���ṩ�ˏ��������p��(sh��)��(j��)���Q�h(hu��n)������O(sh��)Ӌ�߿���ͨ�^I/O Designer ��(chu��ng)��HDL ��̖��ԭ��D��̖�����PCB ����Ҏ(gu��)�t���������_늚���Ϣ�������FPGA ���ֲ����s���ļ��ȶ�N��(sh��)��(j��)����������f�oHDL���FPGA ���ֲ���������PCB �ȸ����O(sh��)Ӌ���̣���Ч�،��F(xi��n)�ˏĸ����O(sh��)Ӌ���оƬ�O(sh��)Ӌ��ϵ�y(t��ng)�O(sh��)Ӌ�ğo�p㕽ӡ�

�s�̮a(ch��n)Ʒ�аl(f��)����I/O Designer ߀���Դ_��FPGA �cPCB�����O(sh��)Ӌ��형��M��������Դ���ȿs�̮a(ch��n)Ʒ�аl(f��)�������������FPGA �cPCB �����O(sh��)Ӌ�^�����������ʹijһ�r��FPGA ���_�����ѽ�(j��ng)�_�������S���Ŀ���Mչ����F(xi��n)PGA ���̎���PCB���̎��S�r�����ܸ���(j��)�Լ�����Ҫ�Ĺ��_����������������N��r�ܳ�Ҋ��

���O(sh��)Ӌ������������a(ch��n)Ʒ�{(di��o)ԇ�����M�A����������ijЩģ�K���ܵ����¶��x����(d��o)����̖�ĸ�׃��������ȻӰ푹��_����;

HDL ���a��׃��������Ҫ��FPGA ���²��ֲ������ԭ�еĹ��_���䱻��y;

��PCB �O(sh��)Ӌ�r���������˸���BGA ���b�IJ������l���M�е��������_�W(w��ng)�j(lu��)���Q����������ʹFPGA ���_�����{(di��o)��I/O Designer �����ԄӱO(ji��n)�yÿλ�O(sh��)Ӌ�ɆT�����_����������������������Ϣ���f�o�����ɆT����ڵõ����S������Ԅӌ� �����ɆT�Ĕ�(sh��)��(j��)�M�и��£��_�����_�c��̖��ӳ����Ϣ��FPGA �cPCB �O(sh��)Ӌ�����Ї���һ��������

ԭ��D�c��̖

I/O Designer �Ԏ�һ����ӆ�Ƶ�ԭ��D��̖��Symbol���c���_��Pin�����Ύ죬֧�����кϺ����I(y��)�˜ʣ�IEEE/JEDEC���Ĺ��_��̖����Symbol ��Pin �����ε���Ϣ�����O(sh��)Ӌ�߿��Ը���(j��)��Ҫӆ��Symbol ��Pin ���Π�������

I/O Designer ���ݶ�N�ļ���ʽ��ԭ��D�cSymbol���Ɍ��Լ���(chu��ng)����ԭ��D��Symbol��(d��o)����Design Architect�������Board Archite��DxDesigner�����Design Capture�������Design View�ȭh(hu��n)����������ͬ�r֧��EDIF������XML �ȸ�ʽ��ԭ��D��Symbol �ļ��Č�(d��o)�롣